# / 日 JAPAN PATENT OFFICE

別紙添付の書類に記載されている事項は下記の出願書類に記載されて いる事項と同一であることを証明する。

This is to certify that the annexed is a true copy of the following application as filed with this Office 出願年月日

Date of Application:

2001年 1月30日

出願番号 Application Number:

特願2001-021930

出 人 Applicant(s):

セイコーエプソン株式会社 ヘイロー エルエスアイ デザイン ノロジー インコーポレイテッド アンド デバイステク

2001年 9月28日

特許庁長官 Commissioner, Japan Patent Offic

【書類名】

特許願

【整理番号】

EP-0275301

【提出日】

平成13年 1月30日

【あて先】

特許庁長官殿

【国際特許分類】 H01L 21/8247

【発明者】

【住所又は居所】

長野県諏訪市大和3丁目3番5号 セイコーエプソン株

式会社内

【氏名】

蝦名 昭彦

【発明者】

【住所又は居所】 長野県諏訪市大和3丁目3番5号 セイコーエプソン株

式会社内

【氏名】

丸尾 豊

【特許出願人】

【識別番号】 000002369

【氏名又は名称】 セイコーエプソン株式会社

【代理人】

【識別番号】

100090479

【弁理士】

【氏名又は名称】

井上 一

【電話番号】

03-5397-0891

【選任した代理人】

【識別番号】 100090387

【弁理士】

【氏名又は名称】 布施 行夫

【電話番号】

03-5397-0891

【選任した代理人】

【識別番号】 100090398

【弁理士】

【氏名又は名称】 大渕 美千栄

【電話番号】

03-5397-0891

【手数料の表示】

【予納台帳番号】 039491

【納付金額】

21,000円

【提出物件の目録】

【物件名】

明細書 1

【物件名】

図面 1

【物件名】

要約書 1

【包括委任状番号】 9402500

. . . . . . . . .

【プルーフの要否】

要

#### 【書類名】 明細書

【発明の名称】 不揮発性半導体記憶装置を含む半導体集積回路装置 【特許請求の範囲】

【請求項1】 不揮発性半導体記憶装置が複数の行および列に格子状に配列 されたメモリセルアレイを有する半導体集積回路装置であって、

前記不揮発性半導体記憶装置は、

半導体層上に第1ゲート絶縁層を介して形成されたワードゲートと、

前記半導体層に形成された、ソース領域またはドレイン領域を構成する不純物 拡散層と、

前記ワードゲートの一方の側面および他方の側面に沿ってそれぞれ形成された 、サイドウォール状の第1および第2コントロールゲートと、を含み、

前記第1コントロールゲートは、前記半導体層に対して第2ゲート絶縁層を介して、かつ、前記ワードゲートに対してサイド絶縁層を介して配置され、

前記第2コントロールゲートは、前記半導体層に対して第2ゲート絶縁層を介して、かつ、前記ワードゲートに対してサイド絶縁層を介して配置され、

前記第1および第2コントロールゲートは、それぞれ第1方向に連続して配置 され、かつ、

前記第1方向と交差する第2方向に対して隣り合う1組の第1および第2コントロールゲートは、共通コンタクト部に接続されている、半導体集積回路装置。

【請求項2】 請求項1において、

前記コントロールゲートは、前記不純物拡散層が延びる方向と同じ方向に連続 する導電層から構成される、半導体集積回路装置。

【請求項3】 請求項1または2において、

前記共通コンタクト部は、前記第1および第2コントロールゲートと連続し、 かつ同じ材質の導電層を有する、半導体集積回路装置。

【請求項4】 請求項1ないし3のいずれかにおいて、

前記共通コンタクト部は、前記半導体層上に形成された絶縁層と、該絶縁層上 に形成された導電層と、該導電層上に形成されたキャップ層とを有する、半導体 集積回路装置。

【請求項5】 請求項4において、

前記絶縁層は、第1酸化シリコン層、窒化シリコン層、および第2酸化シリコン層の積層体からなる、半導体集積回路装置。

【請求項6】 請求項1ないし5のいずれかにおいて、

前記ワードゲートと前記コントロールゲートとの間に位置する前記サイド絶縁 層は、その上端が前記半導体層に対して前記コントロールゲートより上に位置す る、半導体集積回路装置。

【請求項7】 請求項1ないし6のいずれかにおいて、

隣り合う前記第1および第2コントロールゲートは、埋込み絶縁層によって覆われ、該埋込み絶縁層は、該第1および第2コントロールゲートに接して配置された、対向する2つの前記サイド絶縁層の相互間に形成された、半導体集積回路装置。

【請求項8】 請求項1ないし7のいずれかにおいて、

前記共通コンタクト部は、前記不純物拡散層の端部に隣接して設けられた、半 導体集積回路装置。

【請求項9】 請求項8において、

前記共通コンタクト部は、複数配列された前記不純物拡散層に対して、該不純物拡散層の一方の側の端部と他方の側の端部とにおいて交互に設けられた、半導体集積回路装置。

【請求項10】 請求項1ないし9のいずれかにおいて、

前記メモリセルアレイは複数のブロックに分割され、前記第1方向に隣り合う ブロックの前記不純物拡散層は、前記半導体層内に形成されたコンタクト用不純 物拡散層を介して接続された、半導体集積回路装置。

【請求項11】 請求項1ないし10のいずれかにおいて、

前記第2ゲート絶縁層は、第1酸化シリコン層、窒化シリコン層、および第2 酸化シリコン層の積層体からなる、半導体集積回路装置。

【請求項12】 請求項1ないし11のいずれかにおいて、

前記サイド絶縁層は、第1酸化シリコン層、窒化シリコン層、および第2酸化

シリコン層からなる、半導体集積回路装置。

【発明の詳細な説明】

[0001]

【発明の属する技術分野】

本発明は、不揮発性半導体記憶装置、特に1つのワードゲートに対して2つの 電荷蓄積領域を有する不揮発性半導体記憶装置がアレイ状に配置された半導体集 積回路装置に関する。

[0002]

【背景技術および発明が解決しようとする課題】

不揮発性半導体記憶装置のひとつのタイプとして、チャネルとゲートとの間の ゲート絶縁層が酸化シリコン層と窒化シリコン層との積層体からなり、前記窒化 シリコン層に電荷がトラップされるMONOS (Metal Oxide Nitride Oxide Sub strate) 型がある。

[0003]

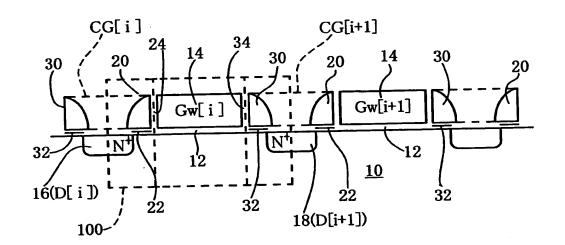

MONOS型の不揮発性半導体記憶装置として、図16に示すデバイスが知られている(文献: Y. Hayashi, et al , 2000 Symposium on VLSI Technology Digest of Technical Papers p. 122-p. 123)。

[0004]

このMONOS型のメモリセル100は、半導体基板10上に第1ゲート絶縁層12を介してワードゲート14が形成されている。そして、ワードゲート14の両サイドには、それぞれサイドウォール状の第1コントロールゲート20および第2コントロールゲート30が配置されている。第1コントロールゲート20の底部と半導体基板10との間には、第2ゲート絶縁層22が存在し、第1コントロールゲート20の側面とワードゲート14との間にはサイド絶縁層24が存在する。同様に、第2コントロールゲート30の底部と半導体基板10との間には、第2ゲート絶縁層32が存在し、第2コントロールゲート30の側面とワードゲート14との間にはサイド絶縁層34が存在する。そして、隣り合うメモリセルの、対向するコントロールゲート20とコントロールゲート30との間の半導体基板10には、ソース領域またはドレイン領域を構成する不純物拡散層16,1

8が形成されている。

[0005]

このように、ひとつのメモリセル100は、ワードゲート14の側面に2つの MONOS型メモリ素子を有する。そして、これらの2つのMONOS型メモリ素子は独立 に制御でき、したがって、メモリセル100は、2ビットの情報を記憶することができる。

[0006]

このMONOS型のメモリセルの動作は、以下のようにして行われる。メモリセル 100の一方のコントロールゲートは、他方のコントロールゲートをオーバライ ド電圧にバイアスすることで、書き込みおよび読み出しをそれぞれ独立に選択す ることができる。

[0007]

書き込み(プログラム)については、図16に示すCG [i+1] の左側の第2ゲート絶縁層(ONO膜)32に電子を注入する場合を用いて説明する。この場合、ビット線(不純物拡散層)18(D[i+1])は、4~5 Vのドレイン電圧にバイアスされている。コントロールゲート30(CG[i+1])は、ホットエレクトロンをコントロールゲート30(CG[i+1])の左側の第2ゲート絶縁層32に注入させるために、5~7 Vにバイアスされる。ワードゲート14(Gw[i]およびGw[i+1])に接続されるワード線は、書き込み電流を所定値(~10μA)に限定するために、ワードゲートのしきい値より少し高い電圧にバイアスされる。コントロールゲート20(CG[i])は、オーバーライド電圧にバイアスされる。このオーバーライド電圧によって、記憶状態に関係なく、コントロールゲート20(CG[i])の下のチャネルを導通させることができる。左側のビット線16(D[i])は、グランド電圧にバイアスされる。そして、他の選択されないメモリセルのコントロールゲートおよび拡散層は、グランド電圧に設定される。

[0008]

消去では、蓄積された電荷(電子)は、ホットホールの注入によってうち消される。ホットホールは、ビット拡散層18の表面でB-Bトンネリングによって

発生させることができる。このとき、コントロールゲートの電圧Vcgは負電圧  $(-5\sim-6V)$  に、ビット拡散層の電圧は $5\sim6V$ にバイアスされる。

[0009]

この文献では、上述したMONOS型のメモリセルによれば、ひとつのメモリセル内に独立に制御可能な2つのプログラミングサイトを有し、3 F  $^2$  のビット密度 (bit density) を達成できることが記載されている。

[0010]

本発明の目的は、2つのコントロールゲートを有するMONOS型の不揮発性半導体記憶装置を含む半導体集積回路装置において、サイドウォール状コントロールゲートのコンタクト構造を提供することにある。

[0011]

【課題を解決するための手段】

本発明にかかる半導体集積回路装置は、不揮発性半導体記憶装置が複数の行および列に格子状に配列されたメモリセルアレイを有する半導体集積回路装置であって、

前記不揮発性半導体記憶装置は、

半導体層上に第1ゲート絶縁層を介して形成されたワードゲートと、

前記半導体層に形成された、ソース領域またはドレイン領域を構成する不純物 拡散層と、

前記ワードゲートの一方の側面および他方の側面に沿ってそれぞれ形成された 、サイドウォール状の第1および第2コントロールゲートと、を含み、

前記第1コントロールゲートは、前記半導体層に対して第2ゲート絶縁層を介して、かつ、前記ワードゲートに対してサイド絶縁層を介して配置され、

前記第2コントロールゲートは、前記半導体層に対して第2ゲート絶縁層を介して、かつ、前記ワードゲートに対してサイド絶縁層を介して配置され、

前記第1および第2コントロールゲートは、それぞれ第1方向に連続して配置 され、かつ、

前記第1方向と交差する第2方向に対して隣り合う1組の第1および第2コントロールゲートは、共通コンタクト部に接続されている。

[0012]

この半導体集積回路装置によれば、サイドウォール状のコントロールゲートは 、1組ごとに、共通コンタクト部に接続されているので、幅の小さいコントロー ルゲートとの電気的接続を確実にとることができる。

[0013]

本発明の半導体集積回路装置は、以下の各種態様をとりうる。

[0014]

(A) 前記コントロールゲートは、前記不純物拡散層が延びる方向と同じ方向 に連続する導電層から構成される。

[0015]

(B) 前記共通コンタクト部は、前記第1および第2コントロールゲートと同じ工程で形成され、したがって、該第1および第2コントロールゲートと連続し、かつ同じ材質の導電層を有する。

[0016]

(C) 前記共通コンタクト部は、前記半導体層上に形成された絶縁層と、該絶縁層上に形成された導電層と、該導電層上に形成されたキャップ層とを有することができる。そして、前記絶縁層は、前記ワードゲートと前記コントロールゲートとの間に位置する前記サイド絶縁層と同じ工程で形成でき、第1酸化シリコン層、窒化シリコン層、および第2酸化シリコン層の積層体から構成できる。

[0017]

(D) 前記ワードゲートと前記コントロールゲートとの間に位置する前記サイド絶縁層は、その上端が前記半導体層に対して前記コントロールゲートより上に位置することが望ましい。この構成により、前記コントロールゲートを覆う埋込み絶縁層を確実に形成できる。すなわち、隣り合う前記第1および第2コントロールゲートは、埋込み絶縁層によって覆われ、該埋込み絶縁層は、該第1および第2コントロールゲートに接して配置された、対向する2つの前記サイド絶縁層の相互間に形成される。

[0018]

(E) 前記共通コンタクト部は、前記不純物拡散層の端部に隣接して設けるこ

とができる。そして、前記共通コンタクト部は、複数配列された前記不純物拡散 層に対して、該不純物拡散層の一方の側の端部と他方の側の端部とにおいて交互 に設けることができる。

[0019]

(F) 前記メモリセルアレイは複数のブロックに分割されることができ、前記 第1方向に隣り合うブロックの前記不純物拡散層は、前記半導体層内に形成され たコンタクト用不純物拡散層を介して接続されることができる。

[0020]

(G)前記第2ゲート絶縁層は、第1酸化シリコン層、窒化シリコン層、および第2酸化シリコン層の積層体から構成できる。また、前記ワードゲートと前記コントロールゲートとの間に位置する前記サイド絶縁層は、第1酸化シリコン層、窒化シリコン層、および第2酸化シリコン層から構成できる。これらの第2ゲート絶縁層およびサイド絶縁層は、同じ工程で形成できる。

[0021]

【発明の実施の形態】

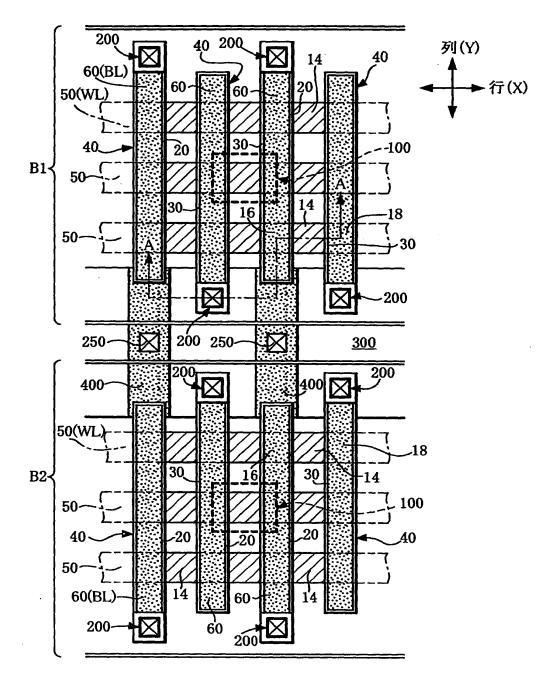

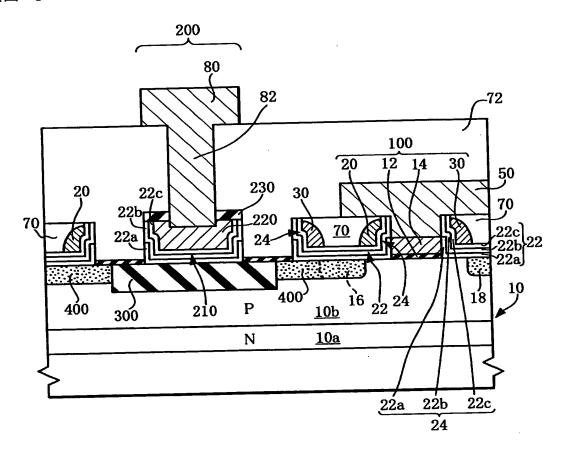

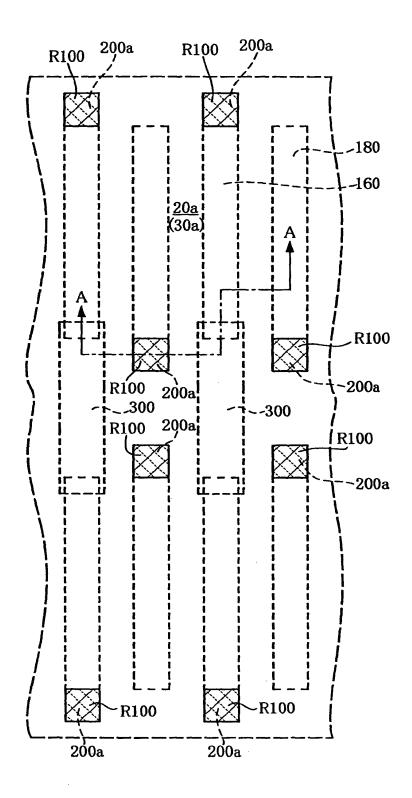

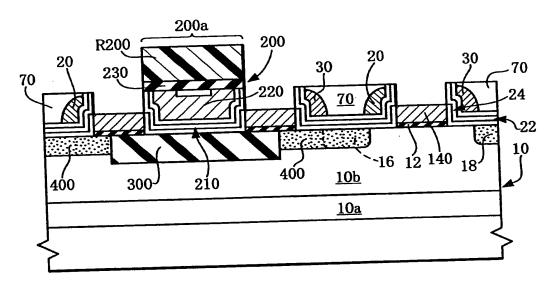

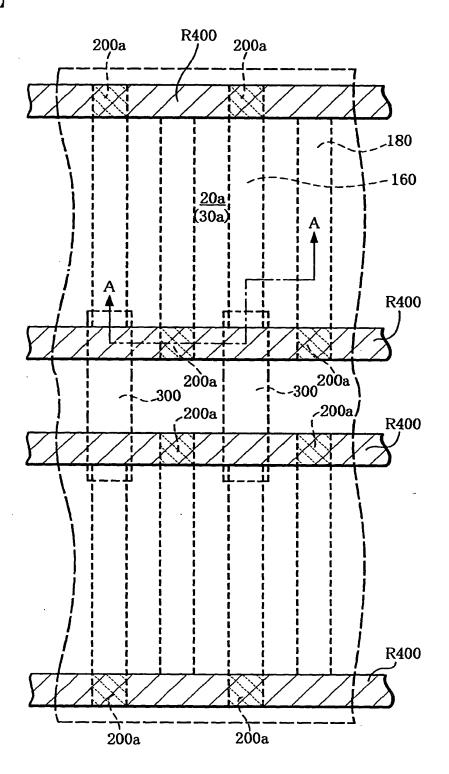

図1は、本発明の不揮発性半導体記憶装置を含む半導体集積回路装置のレイアウトを模式的に示す平面図であり、図2は、図1のA-A線に沿った部分を模式的に示す断面図である。

[0022]

本実施の形態に係る半導体集積回路装置は、前述した公知の不揮発性半導体記憶装置(メモリセル)100が、複数の行および列に格子状に配列されてメモリセルアレイを構成している。

[0023]

(デバイスの構造)

まず、図1を参照しながら、本実施の形態の半導体集積回路装置のレイアウト について説明する。

[0024]

図1においては、第1のブロックB1と、これに隣接する第2のブロックB2とを示している。第1のブロックB1と第2のブロックB2とは素子分離領域3

00によって分離されている。各ブロックB1, B2においては、行方向(X方向)に伸びる複数のワード線50(WL)と、列方向(Y方向)に伸びる複数のビット線60(BL)とが設けられている。ワード線50は、ワードゲート14に接続して設けられ、ビット線60は不純物拡散層16, 18によって構成されている。

## [0025]

第1および第2コントロールゲート20,30は、それぞれ、列方向に、すなわち、ワードゲート14の側面に沿って伸びる連続した導電層40から構成されている。本実施の形態では、各不純物拡散層16,18を囲むように、第1,第2コントロールゲート20,30を構成する導電層40が形成されている。第1,第2コントロールゲート20,30の一方の端部は連続し、他方の端部は、1つの共通コンタクト部200に接続されている。したがって、各第1,第2コントロールゲート20,30は、メモリセルのコントロールゲートの機能と、列方向に配列された各コントロールゲートを接続する配線としての機能を有する。

# [0026]

単一のメモリセル100は、1つのワードゲート14と、このワードゲート14の両側の半導体基板内にある第1,第2コントロールゲート20,30と、これらのコントロールゲート20,30の外側にある不純物拡散層16,18とを有する。そして、不純物拡散層16,18は、それぞれ隣り合うメモリセル100によって共有される。

## [0027]

列方向に隣接するブロックB1およびB2において、不純物拡散層16は、共通コンタクト部200を有さない側において、半導体基板内に形成されたコンタクト用不純物拡散層400によって接続されている。このコンタクト用不純物拡散層400上には、ビット線60とのコンタクト250が形成される。同様に、列方向に隣接する不純物拡散層18は、図示しないコンタクト用不純物拡散層によって接続されている。

# [0028]

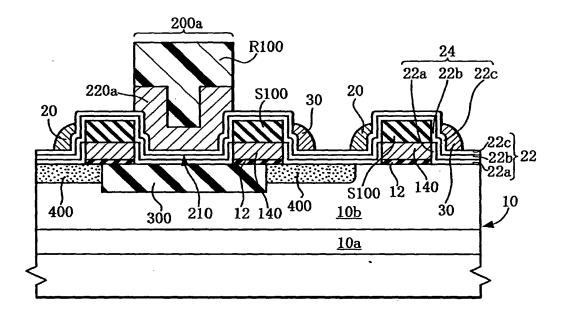

次に、図2を参照しながら、半導体集積回路装置の断面構造について説明する

[0029]

メモリセル100は、半導体基板10の主面上に第1ゲート絶縁層12を介して形成されたワードゲート14と、半導体基板10内に形成された、ソース領域またはドレイン領域を構成する不純物拡散層16,18と、ワードゲート14の両側に沿ってそれぞれ形成された、サイドウォール状の第1および第2のコントロールゲート20,30とを有する。本実施の形態では、半導体基板10は、N型の第1ウェル10aと、この第1ウェル10a内に形成されたP型の第2ウェル10bとを有する。第1ウェル10aは、第2ウェル10bを半導体基板10の他の領域から電気的に分離する機能を有する。

[0030]

第1コントロールゲート20は、半導体基板10の第2ウェル10bに対して第2ゲート絶縁層22を介して配置され、かつ、ワードゲート14の一方の側面に対してサイド絶縁層24を介して配置されている。同様に、第2コントロールゲート30は、半導体基板10の第2ウェル10bに対して第2ゲート絶縁層22を介して配置され、かつ、ワードゲート14の他方の側面に対してサイド絶縁層24を介して配置されている。そして、第2ゲート絶縁層22およびサイド絶縁層24は、第1酸化シリコン層22a、窒化シリコン層22bおよび第2酸化シリコン層22cから構成されている。第2ゲート絶縁層22は、電荷の蓄積領域として機能する。そして、第1酸化シリコン層22aは、主としてキャリア(たとえば電子)が通過するトンネル膜として機能し、窒化シリコン層22bは、主としてキャリアをトラップする電荷蓄積層として機能する。

[0031]

さらに、ワードゲート14の両サイドに形成されたサイド絶縁層24,24は、ワードゲート14と、コントロールゲート20,30とをそれぞれ電気的に分離する機能を有する。そのため、サイド絶縁層24はかかる機能を有していれば、その構造は特に限定されない。本実施の形態では、サイド絶縁層24と第2ゲート絶縁層22とは、同じ成膜工程で形成され、同じ層構造を有する。さらに、サイド絶縁層24は、その上端が半導体基板10に対してコントロールゲート2

0,30より上に位置するように形成されている。そして、隣り合うメモリセル 100において、隣接する第1コントロールゲート20と第2コントロールゲート30との間には、埋め込み絶縁層70が形成されている。この埋め込み絶縁層70は、少なくともコントロールゲート20,30が露出しないようにこれを覆っている。

### [0032]

共通コンタクト部200は、コントロールゲート20,30に電圧を印加させるためのものであり、素子分離領域300上に形成された絶縁層210、導電層220およびキャップ層230から構成されている。絶縁層210は、第2ゲート絶縁層22およびサイド絶縁層24と同じ工程で形成され、第1酸化シリコン層22a,窒化シリコン層22bおよび第2酸化シリコン層22cの積層体から構成されている。導電層220は、第1,第2コントロールゲート20,30と同一工程で形成される。そして、導電層220は、コントロールゲート20,30と連続しており、かつこれらと同じ材質を有する。さらに、キャップ層230は、たとえば窒化シリコン層などの絶縁層から構成されている。キャップ層230は、コントロールゲート20,30および導電層220のパターニングにおいて、マスク層として機能する。

#### [0033]

メモリセル100および共通コンタクト部200などが形成された半導体基板10上には、層間絶縁層72が形成されている。そして、層間絶縁層72には、コンタクト部200の導電層220に到達するコンタクトホール内に導電層82が充填され、この導電層82は層間絶縁層72上に形成された配線層80と接続されている。

#### [0034]

この実施の形態にかかる半導体集積回路装置によれば、サイドウォール状のコントロールゲート20,30は、1組ごとに、コントロールゲート20,30と連続したパッド状の共通コンタクト部200と接続されているので、コントロールゲートとの電気的接続を確実にとることができる。すなわち、本発明のコントロールゲートは、サイドウォール状の形状を有し、その幅は通常0.1μmより小

さく、したがって、このようなコントロールゲートとの電気的接続を確保することは重要な課題となる。本実施の形態では、コントロールゲートとの電気的コンタクトを上記の共通コンタクト部によって必要最小限の面積で確保できる。

[0035]

(半導体集積回路装置の製造方法)

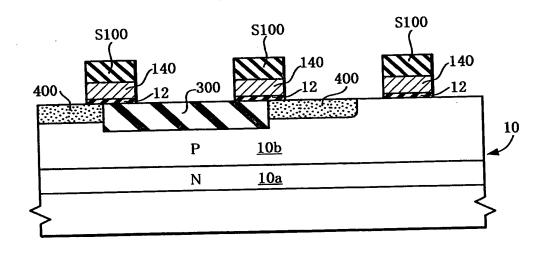

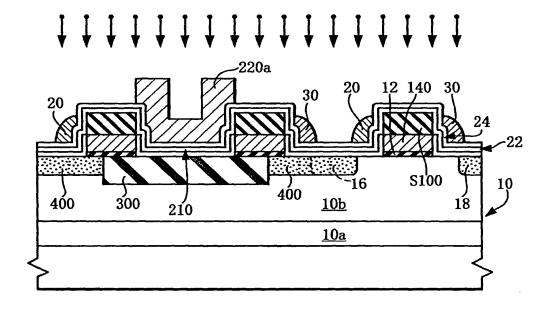

次に、図3~図14を参照しながら、本実施の形態に係る半導体集積回路装置の製造方法について説明する。各断面図は、図1のA-A線に沿った部分に対応する。図3~図14において、図1で示す部分と実質的に同じ部分には同じ符号を付し、重複する記載は省略する。

[0036]

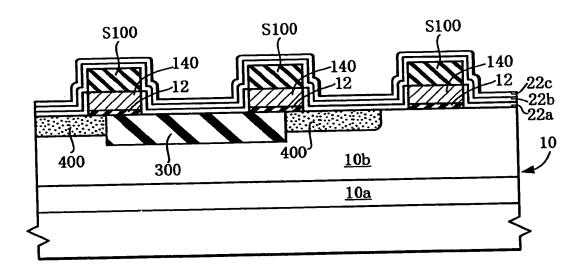

(1) 図3および図4に示すように、まず、半導体基板10の表面に、LOCOS法あるいはトレンチアイソレーション法などによって素子分離領域300を形成する。ついで、深いN型の第1ウエル10aおよび第1ウエル10aより浅いP型の第2ウエル10bを形成する。ついで、ビット線60のためのコンタクト210(図1参照)を形成するためのコンタクト用不純物拡散層400を半導体基板10内に形成する。

[0037]

ついで、半導体基板10の表面に第1ゲート絶縁層12、ドープトポリシリコンからなるワードゲート層140および後のCMP工程におけるストッパ層S100を形成する。ストッパ層S100としては、たとえば窒化シリコン層などを用いることができる。

[0038]

ワードゲート層140およびストッパ層S100の積層体は、図4に示すように、開口部160,180を除いて半導体基板10上に全面的に形成される。開口部160,180は、後のイオン注入によって不純物拡散層16,18が形成される領域にほぼ対応している。図4におけるA-A線は、図1のA-A線に対応している。そして、後の工程で、開口部160,180の縁部に沿ってサイド・絶縁層とコントロールゲートとが形成される。

[0039]

(2) 図5に示すように、ワードゲート層140およびストッパ層S100の積層体が形成された半導体基板10上に、第1酸化シリコン層22a、窒化シリコン層22bおよび第2酸化シリコン層22cを全面的に順次堆積させる。第1酸化シリコン層22aは、たとえば熱酸化法を用いて成膜することができる。窒化シリコン層22bは、たとえばアンモニア雰囲気においてアニール処理した後、CVD法などによって成膜することができる。第2酸化シリコン層22cは、CVD法、たとえば高温酸化法を用いて成膜することができる。これらの各層を成膜した後アニール処理を行い、各層を緻密化することが好ましい。

#### [0040]

これらの第1酸化シリコン層22a、窒化シリコン層22bおよび第2酸化シリコン層22cは、後のパターニングによって、図2に示すように、コントロールゲート20,30のための第2ゲート絶縁層22およびサイド絶縁層24、ならびに共通コンタクト部200の絶縁層210を構成する。

#### [0041]

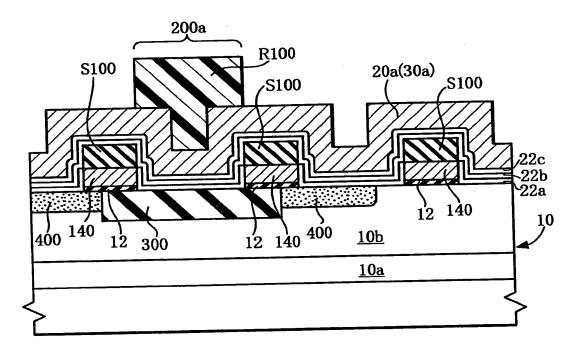

(3) 図6に示すように、ドープトポリシリコン層20a(30a)を、第2酸化シリコン層22C上に全面的に形成する。ドープトポリシリコン層20a(30a)は、後にパターニングされて、コントロールゲート20,30を構成する導電層40(図1参照)および共通コンタクト部200の導電層220(図2参照)を構成する。

# [0042]

ついで、共通コンタクト部が形成される領域(以下、「共通コンタクト部の形成領域」という)200aに、レジスト層R100を形成する。この実施の形態では、このレジスト層R100は、図7に示すように、共通コンタクト部の形成領域200aに対応した位置に設けられている。

#### [0043]

(4) 図8に示すように、ドープトポリシリコン層20aを異方性エッチングによって全面的にエッチングすることにより、第1および第2コントロールゲート20,30および共通コンタクト部のための導電層220aを形成する。すなわち、この工程では、ワードゲート層140の開口部160,180(図4参照

)の側面に沿って、サイド絶縁層24を介在させた状態で、第2ゲート絶縁層2 2上にサイドウォール状のコントロールゲート20,30が形成される。そして、これと同時に、レジスト層R100でマスクされた部分には、コントロールゲート20,30と連続する、共通コンタクト部のための導電層220aが形成される。ついで、レジスト層R100は、溶解あるいはアッシングなどの方法で除去される。

#### [0044]

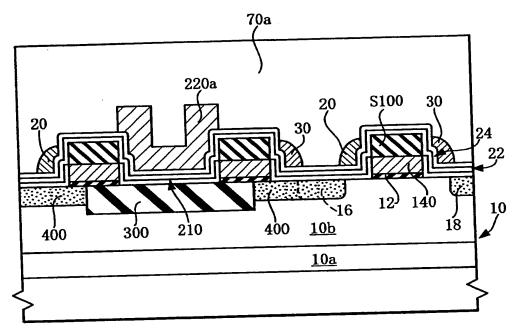

(5) 図9に示すように、不純物、たとえばN型不純物を全面的にイオン注入することにより、第2ウエル10b内に、ソース領域またはドレイン領域を構成する不純物拡散層16,18を形成する。なお、必要に応じて、不純物拡散層16,18を形成する領域上の第2絶縁層を除去することができる。そして、不純物拡散層16,18の露出部分にチタン、コバルトなどのシリサイド層を形成することができる。

#### [0045]

(6) 図10に示すように、第1,第2コントロールゲート20,30および 導電層220aなどが形成された半導体基板10上に、酸化シリコン、窒化酸化 シリコンなどの絶縁層70aを全面的に形成する。

#### [0046]

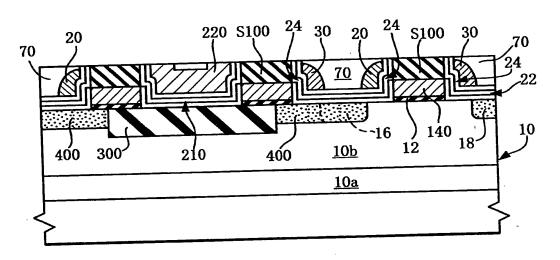

(7) 図11に示すように、絶縁層70aをCMP法を用いて、ストッパ層S100が露出するまで平坦化を行う。このとき、ワードゲート層140およびストッパ層S100の側面に形成されたサイド絶縁層24は、コントロールゲート20,30より上に突出する状態で残される。そして、コントロールゲート20,30をはさんで対向するサイド絶縁層24,24間には埋込み絶縁層70が形成される。この工程によって、第1,第2コントロールゲート20,30が埋込み絶縁層70によって完全に覆われるとともに、共通コンタクト部を構成する導電層220の少なくとも一部が露出する。

# [0047]

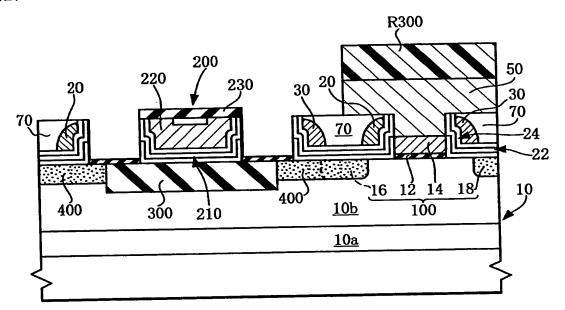

(8) 図12に示すように、平坦化された埋め込み絶縁層70およびストッパ 層S100を含む積層体の表面全体に窒化シリコン層などの絶縁層230aを形 成する。ついで、図13に示すように、共通コンタクト部の形成領域200aに レジスト層R200を形成し、これをマスクとして絶縁層230aをパターニン グすることで、キャップ層230を形成する。ついで、レジスト層R200を公 知の方法で除去する。

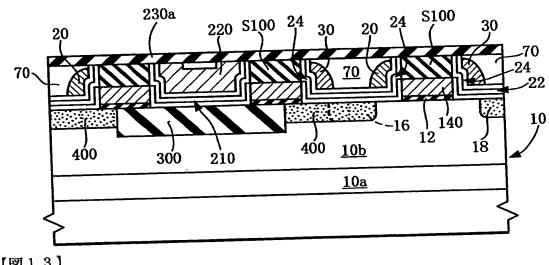

[0048]

(9)図14に示すように、ドープトポリシリコン層、金属層あるいはシリサイドなどの合金層からなる導電層を形成した後、レジスト層R300を形成し、前記導電層をパターニングすることにより、ワード線50を形成する。さらに、レジスト層R300あるいはワード線50が金属層の場合にはこれをマスクとして、ドープトポリシリコンからなるワードゲート層140をパターニングすることにより、アレイ状に配列したワードゲート14を形成する。

[0049]

続いて、図2に示すように、公知の方法で層間絶縁層72を形成した後、共通コンタクト部200と接続された導電層82および配線層80を形成する。

[0050]

以上の工程により、図1に示す半導体集積回路装置を製造することができる。

[0051]

この製造方法によれば、特に工程数を増加させることなく、サイドウォール状のコントロールゲート20,30とともに共通コンタクト部200を形成できる。そして、共通コンタクト部200は、少なくとも不純物拡散層16,18の幅に近いサイズを有することができ、充分に大きなコンタクト面積を確保できる。したがって、本発明では、充分なコントクト領域をとりにくいサイドウォール状のコントロールゲート20,30であっても、共通コンタクト部200を介して確実な電気的接続をとることができる。

[0052]

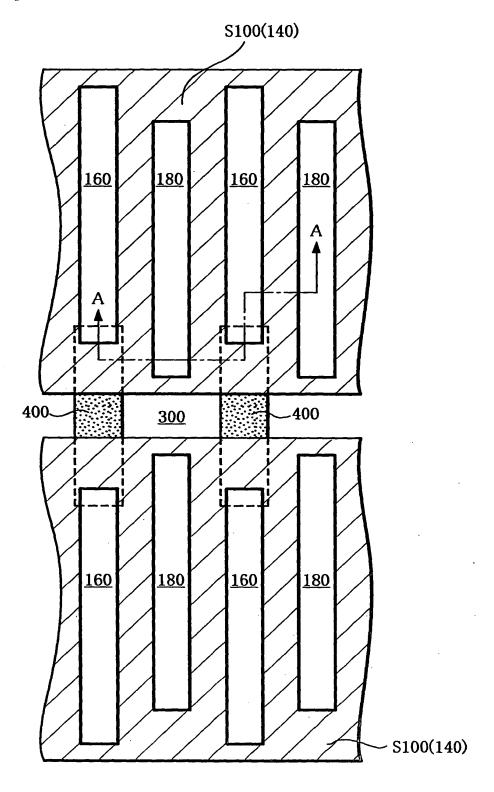

(変形例)

次に、上記実施の形態の変形例について、図15を参照して説明する。図15 は、上記実施の形態の工程(3)における平面図を示し、図7に相当する。図1 5において図7に示す部分と実質的に同じ部分には同じ符号を付して、その説明 を省略する。

[0053]

図7に示す例においては、共通コンタクト部の形成領域200aに対応する部分のみにレジスト層R100を形成している。これに対して図15に示す例においては、行方向に複数存在する共通コンタクト部の形成領域200a上を覆うように、連続するレジスト層R400を用いている。このような連続するレジスト層R400を用いることで、図7に示す分離されたレジスト層R100を用いた場合に比べて、リソグラフィーにおける光の近接効果の影響を緩和でき、より正確なパターニングができる点で有利である。

[0054]

この例の場合、共通コンタクト部の形成領域200a以外の部分にもドープトポリシリコン層20a(30a)が残るが、不要な部分は上記実施の形態の工程(9)でワードゲート14をパターニングする際に、キャップ層230をマスクとして同時に除去できる。

[0055]

以上、本発明の一実施の形態について述べたが、本発明はこれに限定されず、本発明の発明の要旨の範囲内で種々の態様をとりうる。たとえば、上記実施の形態では、半導体層としてバルク状の半導体基板を用いたが、SOI基板の半導体層を用いてもよい。

【図面の簡単な説明】

【図1】

本発明の実施の形態にかかる半導体集積回路装置のレイアウトを模式的に示す平面図である。

【図2】

図1のA-A線に沿った部分を模式的に示す断面図である。

【図3】

図1および図2に示す半導体集積回路装置の製造方法の一工程を示す断面図である。

【図4】

図3に示す半導体集積回路装置の製造方法の一工程を示す平面図である。

【図5】

図1および図2に示す半導体集積回路装置の製造方法の一工程を示す断面図である。

【図6】

図1および図2に示す半導体集積回路装置の製造方法の一工程を示す断面図である。

【図7】

図6に示す半導体集積回路装置の製造方法の一工程を示す平面図である。

【図8】

図1および図2に示す半導体集積回路装置の製造方法の一工程を示す断面図で ある。

【図9】

図1および図2に示す半導体集積回路装置の製造方法の一工程を示す断面図である。

【図10】

図1および図2に示す半導体集積回路装置の製造方法の一工程を示す断面図で ある。

【図11】

図1および図2に示す半導体集積回路装置の製造方法の一工程を示す断面図で ある。

【図12】

図1および図2に示す半導体集積回路装置の製造方法の一工程を示す断面図で ある。

【図13】

図1および図2に示す半導体集積回路装置の製造方法の一工程を示す断面図である。

【図14】

図1および図2に示す半導体集積回路装置の製造方法の一工程を示す断面図で

ある。

#### 【図15】

本発明にかかる半導体集積回路装置の製造方法の一工程の変形例を示す平面図である。

#### 【図16】

公知のMONOS型メモリセルを示す断面図である。

#### 【符号の説明】

- 10 半導体基板

- 10a, 10b ウェル

- 12 第1ゲート絶縁層

- 14 ワードゲート

- 16,18 不純物拡散層

- 20 第1コントロールゲート

- 20a ドープドポリシリコン層

- 22 第2ゲート絶縁層

- 24 サイド絶縁層

- 30 第2コントロールゲート

- 30a ドープドポリシリコン層

- 50 ワード線

- 60 ビット線

- 70 埋込み絶縁層

- 70a 絶縁層

- 72 層間絶縁層

- 80 配線層

- 100 メモリセル

- 160,180 開口部

- 200 共通コンタクト部

- 200a 共通コンタクト部の形成領域

- 210 絶縁層

- 220, 220a 導電層

- 230 キャップ層

- 300 素子分離領域

- 400 コンタクト用不純物拡散層

- S100 ストッパ層

- R100、R200、R300、R400 レジスト層

【書類名】

図面

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

[図10]

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【書類名】 要約書

【要約】

【課題】 MONOS型の不揮発性半導体記憶装置を含む半導体集積回路装置において、サイドウォール状コントロールゲートのコンタクト構造を提供する。

【解決手段】 半導体集積回路装置は、不揮発性半導体記憶装置(メモリセル) 100が複数の行および列に格子状に配列されたメモリセルアレイを有する。不 揮発性半導体記憶装置は、半導体基板10上に第1ゲート絶縁層12を介して形成されたワードゲート14と、半導体基板10に形成された、ソース領域またはドレイン領域を構成する不純物拡散層16,18と、ワードゲートの一方の側面および他方の側面に沿ってそれぞれ形成された、サイドウォール状の第1および第2コントロールゲート20,30と、を有する。第1および第2コントロールゲートは、それぞれ、半導体基板に対して第2ゲート絶縁層22を介して、かつ、ワードゲート対してサイド絶縁層24を介して配置される。また、第1および第2コントロールゲートは、それぞれ列方向に連続して配置され、かつ、行方向に対して隣り合う1組の第1および第2コントロールゲートは、共通コンタクト部200に接続されている。

【選択図】 図2

【書類名】

出願人名義変更届

【整理番号】

EP-0275301

【提出日】

平成13年 8月 3日

【あて先】

特許庁長官殿

【事件の表示】

【出願番号】

特願2001-21930

【承継人】

【識別番号】

598165507

【氏名又は名称】

ヘイロー エルエスアイ デザイン アンド デバイス

テクノロジー インコーポレイテッド

【承継人代理人】

【識別番号】

100090479

【弁理士】

【氏名又は名称】

井上 一

【電話番号】

03-5397-0891

【承継人代理人】

【識別番号】

100090387

【弁理士】

【氏名又は名称】 布施 行夫

【電話番号】

03-5397-0891

【承継人代理人】

【識別番号】

100090398

【弁理士】

【氏名又は名称】

大渕 美千栄

【電話番号】

03-5397-0891

【手数料の表示】

【予納台帳番号】

039491

【納付金額】

4,200円

【提出物件の目録】

【包括委任状番号】 0110760

【プルーフの要否】 要

# 認定・付加情報

特許出願の番号 特願2001-021930

受付番号 50101149666

書類名 出願人名義変更届

担当官 森吉 美智枝 7577

作成日 平成13年 9月18日

<認定情報・付加情報>

【承継人】

【識別番号】 598165507

【住所又は居所】 アメリカ合衆国 12590 ニューヨーク州、

ワッピンガーズ フォールズ、メイヤーズ コー

ナーズ ロード169

【氏名又は名称】 ヘイロー エルエスアイ デザイン アンド デ

バイステクノロジー インコーポレイテッド

【承継人代理人】 申請人

【識別番号】 100090479

【住所又は居所】 東京都杉並区荻窪5丁目26番13号 荻窪TM

ビル2階 井上・布施合同特許事務所

【氏名又は名称】 井上 一

【承継人代理人】

【識別番号】 100090387

【住所又は居所】 東京都杉並区荻窪5丁目26番13号 荻窪TM

ビル2階 井上・布施合同特許事務所

【氏名又は名称】 布施 行夫

【承継人代理人】

【識別番号】 100090398

【住所又は居所】 東京都杉並区荻窪5丁目26番13号 荻窪TM

ビル2階 井上・布施合同特許事務所

【氏名又は名称】 大渕 美千栄

# 出 願 人 履 歴 情 報

識別番号

[000002369]

1. 変更年月日 1990年 8月20日

[変更理由] 新規登録

住 所 東京都新宿区西新宿2丁目4番1号

氏 名 セイコーエプソン株式会社

## 出願人履歷情報

識別番号

[598165507]

1. 変更年月日 1998年12月 1日

[変更理由] 新規登録

住 所 アメリカ合衆国,ニューヨーク州 12590, ワッピンジャーズ フォールス,オールド ホープウェル ロード 140

氏 名 ヘイロー エルエスアイ デザイン アンド デバイステクノ

ロジー インコーポレイテッド

2. 変更年月日 2001年 7月16日

[変更理由] 住所変更

住 所 アメリカ合衆国 12590 ニューヨーク州、ワッピンガー

ズ フォールズ、メイヤーズ コーナーズ ロード169

氏 名 ヘイロー エルエスアイ デザイン アンド デバイステクノ

ロジー インコーポレイテッド